|

- A Logic Circuit Simulation Library in C++ |

|

- A Logic Circuit Simulation Library in C++ |

Let a and b be input signals to a 1-bit fulladder, and c the carry input. Let S be the sum output, and C the carry output. Then, the truth table for S and C is as shown below.

a | b | c | S | C ---|-----|-----|---------|---- 0 | 0 | 0 | 0 | 0 ---|-----|-----|---------|---- 0 | 0 | 1 | 1 | 0 ---|-----|-----|---------|---- 0 | 1 | 0 | 1 | 0 ---|-----|-----|---------|---- 0 | 1 | 1 | 0 | 1 ---|-----|-----|---------|---- 1 | 0 | 0 | 1 | 0 ---|-----|-----|---------|---- 1 | 0 | 1 | 0 | 1 ---|-----|-----|---------|---- 1 | 1 | 0 | 0 | 1 ---|-----|-----|---------|---- 1 | 1 | 1 | 1 | 1

The code to implement the above logic using conitnuous assignments is as follows.

#include <lcs/bus.h> #include <lcs/tester.h> #include <lcs/simul.h> #include <lcs/changeMonitor.h> using namespace lcs; int main(void) { Bus<1> a, b, c, S, C; // Continuous assignment statements to generate // the sum and carry outputs. The template parameters // indicate the assignment delay. We have used 0 // delay here. S.cass<0>(a&~b&~c | ~a&b&~c | ~a&~b&c | a&b&c); C.cass<0>(a&b&~c | a&~b&c | ~a&b&c | a&b&c); ChangeMonitor<3> inputMonitor((c,b,a), "Input", DUMP_ON); ChangeMonitor<2> outputMonitor((S,C), "Sum", DUMP_ON); Tester<3> tester((c,b,a)); Simulation::setStopTime(1000); Simulation::start(); return 0; }

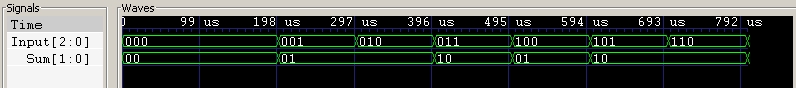

The output when the above program is compiled and run is as below. See this for information on interpreting the output.

At time: 0, Input: 000 At time: 0, Sum: 00 At time: 200, Input: 001 At time: 200, Sum: 01 At time: 300, Input: 010 At time: 400, Input: 011 At time: 400, Sum: 10 At time: 500, Input: 100 At time: 500, Sum: 01 At time: 600, Input: 101 At time: 600, Sum: 10 At time: 700, Input: 110 At time: 800, Input: 111 At time: 800, Sum: 11

Below is the screenshot of the gtkwave plot of the generated VCD file.