|

- A Logic Circuit Simulation Library in C++ |

|

- A Logic Circuit Simulation Library in C++ |

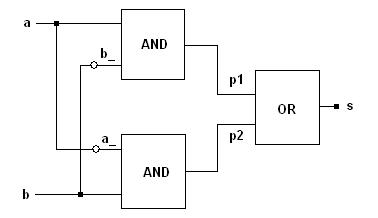

The aim of this example it build and simulate a circuit which is equivalent to an XOR gate for two inputs. The constraints are that we can only use AND, OR and NOT gates to build it. Let a and b be inputs to our circuit. Let s be the output. Then, the boolean function for s is:

s = ab' + a'b

Hence, to generate s from a and b, we require two 2-input AND gates, one 2-input OR gate, and two NOT gates. The circuit diagram is as follows (the small circles/bubbles represent NOT gates):

#include <lcs/bus.h> #include <lcs/not.h> #include <lcs/and.h> #include <lcs/or.h> #include <lcs/tester.h> #include <lcs/simul.h> #include <lcs/changeMonitor.h> int main() { lcs::Bus<1> a, b, a_, b_, p1, p2, s; lcs::Not<> ng1(a_, a), ng2(b_, b); lcs::And<2> ag1(p1, (a,b_)), ag2(p2, (a_,b)); lcs::Or<2> og(s, (p1,p2)); lcs::ChangeMonitor<2> inputMonitor((a,b), "Input", lcs::DUMP_ON); lcs::ChangeMonitor<1> outputMonitor(s, "Output", lcs::DUMP_ON); lcs::Tester<2> tester((a,b)); lcs::Simulation::setStopTime(1000); lcs::Simulation::start(); return 0; }

The output when the above program is compiled and run is as below. See this for information on interpreting the output.

At time: 0, Input: 00 At time: 0, Output: 0 At time: 200, Input: 01 At time: 200, Output: 1 At time: 300, Input: 10 At time: 400, Input: 11 At time: 400, Output: 0

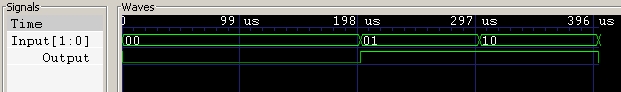

Below is the screenshot of the gtkwave plot of the generated VCD file.