|

- A Logic Circuit Simulation Library in C++ |

|

- A Logic Circuit Simulation Library in C++ |

#include <dflipflop.h>

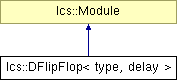

Inheritance diagram for lcs::DFlipFlop< type, delay >:

lcs::POS_EDGE or lcs::NEG_EDGE. lcs::POS_EDGE (which is the default) indicates a positive edge triggered flipflop, where as lcs::NEG_EDGE indicates a negetive edge triggered flipflop. The second template parameter indicates the propogation delay involved in transeffering the data input to the output of the flipflop when triggered.

Public Member Functions | |

| DFlipFlop (const Bus< 1 > &QBus, const InputBus< 1 > &DBus, const InputBus< 1 > &clock) | |

| virtual | ~DFlipFlop (void) |

| virtual void | onPosEdge (int portId) |

| virtual void | onNegEdge (int portId) |

Static Public Attributes | |

| static const int | D = 0 |

| static const int | CLK = 1 |

| static const int | Q = 2 |

| static const int | RST = 3 |

| lcs::DFlipFlop< type, delay >::DFlipFlop | ( | const Bus< 1 > & | QBus, | |

| const InputBus< 1 > & | DBus, | |||

| const InputBus< 1 > & | clock | |||

| ) |

The only explicit constructor. The other constructors, if synthesized by the compiler, are practically useless and hence their use should be avoided.

| QBus | The bus connected to the Q output port of the flipflop. | |

| DBus | The bus connected to the D input port of the flipflop. | |

| clock | The clock input to the flipflop |

| lcs::DFlipFlop< type, delay >::~DFlipFlop | ( | void | ) | [virtual] |

Destructor.

| virtual void lcs::DFlipFlop< type, delay >::onNegEdge | ( | int | portId | ) | [inline, virtual] |

The function which is triggered by the clock input in case of a negetive edge triggered flipflop. User of the class lcs::DFlipFlop will never need to call this function under normal circumstances.

Reimplemented from lcs::Module.

| virtual void lcs::DFlipFlop< type, delay >::onPosEdge | ( | int | portId | ) | [inline, virtual] |

The function which is triggered by the clock input in case of a positive edge triggered flipflop. User of the class lcs::DFlipFlop will never need to call this function under normal circumstances.

Reimplemented from lcs::Module.

const int lcs::DFlipFlop< type, delay >::CLK = 1 [static] |

A static integer which denotes the port corresponding to the clock input to the flipflop.

const int lcs::DFlipFlop< type, delay >::D = 0 [static] |

A static integer which denotes the port corresponding to the D input to the flipflop.

const int lcs::DFlipFlop< type, delay >::Q = 2 [static] |

A static integer which denotes the port corresponding to the output to the flipflop.

const int lcs::DFlipFlop< type, delay >::RST = 3 [static] |

A static integer which denotes the port corresponding to the reset input of the flipflop.