|

- A Logic Circuit Simulation Library in C++ |

|

- A Logic Circuit Simulation Library in C++ |

#include <and.h>

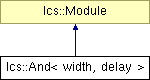

Inheritance diagram for lcs::And< width, delay >:

width denotes the number of lines in the input data bus. In other words, the template parameter width denotes the number of inputs to the AND gate. Hence, one can instantiate an N-input AND gate by setting the template parameter value to N. The second template parameter indicates the propogation delay from the input to the output of the AND gate.

Public Member Functions | |

| And (const Bus< 1 > &output, const InputBus< width > &in1) | |

| virtual | ~And () |

| virtual void | onStateChange (int portId) |

Static Public Attributes | |

| static const int | INPUT = 0 |

| static const int | OUTPUT = 1 |

| lcs::And< width, delay >::And | ( | const Bus< 1 > & | output, | |

| const InputBus< width > & | in1 | |||

| ) |

This is the only meaningfull constructor for the class. A default constructor is not explicitly provided. Moreover, the one synthesized by the compiler is practically useless.

| output | The single line output bus of the gate. | |

| input | The multiline input bus to the gate. | |

| width | The number of lines in the input bus. |

Destructor.

| void lcs::And< width, delay >::onStateChange | ( | int | portId | ) | [virtual] |

Propogates the input data line states to the output when the line states of the input bus change. Specifically, an AND operation is performed on the line states of the data lines of the input bus, and the result is propogated to the single line output bus when a call is made to this function.

Reimplemented from lcs::Module.

const int lcs::And< width, delay >::INPUT = 0 [static] |

A constant integer which denotes the port id for the input port/bus.

const int lcs::And< width, delay >::OUTPUT = 1 [static] |

A constant integer which denotes the port id for the output bus/port.