|

- A Logic Circuit Simulation Library in C++ |

|

- A Logic Circuit Simulation Library in C++ |

In this example, we will illustrate the use of bitselects as module ports. We consider a simple example where in an AND gate module is initialised using bitselects as its input and output arguments.

#include <lcs/lcs.h> using namespace lcs; int main(void) { Bus<3> b; And<2> a1(b[0], (b[1], b[2])); Tester<2> tester((b[1], b[2])); ChangeMonitor<2> input((b[1], b[2]), "Input", DUMP_ON); ChangeMonitor<1> output(b[0], "Output", DUMP_ON); Simulation::setStopTime(1000); Simulation::start(); return 0; }

The following is the output when the above program is compiled and run.

At time: 0, Input: 00 At time: 0, Output: 0 At time: 200, Input: 01 At time: 300, Input: 10 At time: 400, Input: 11 At time: 400, Output: 1

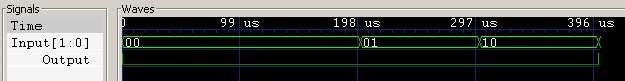

Below is the screenshot of the gtkwave plot of the generated VCD file.