|

- A Logic Circuit Simulation Library in C++ |

|

- A Logic Circuit Simulation Library in C++ |

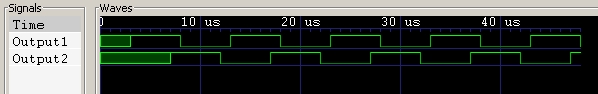

This example will illustrate the propogation delay through the off-the-shelf NOT gates provided in libLCS. Two NOT gates with the clock pulse as inputs are set up. One of the NOT gates has a propogation delay which is more than the clock pulse width, and the other has a propogation delay which is less than clock pulse width.

#include <lcs/not.h> #include <lcs/clock.h> #include <lcs/simul.h> #include <lcs/changeMonitor.h> using namespace lcs; int main() { Bus<> s1, s2; Clock clk = Clock::getClock(); Clock::setPulseWidth(5); // Initialising an NOT gate with a propogation delay of // three system time units. This delay is less than the // pulse width of the clock signal. Not<3> n1(s1, clk); // Initialising an NOT gate with a propogation delay of // seven system time units. This delay is more than the // pulse width of the clock signal. Not<7> n2(s2, clk); // Initialising change monitors to monitor the output of // the two AND gates. ChangeMonitor<> s1m(s1, "Output1", DUMP_ON), s2m(s2, "Output2", DUMP_ON); Simulation::setStopTime(50); Simulation::start(); return 0; }

The output when the above program is compiled and run is as follows.

At time: 3, Output1: 1 At time: 7, Output2: 1 At time: 8, Output1: 0 At time: 12, Output2: 0 At time: 13, Output1: 1 At time: 17, Output2: 1 At time: 18, Output1: 0 At time: 22, Output2: 0 At time: 23, Output1: 1 At time: 27, Output2: 1 At time: 28, Output1: 0 At time: 32, Output2: 0 At time: 33, Output1: 1 At time: 37, Output2: 1 At time: 38, Output1: 0 At time: 42, Output2: 0 At time: 43, Output1: 1 At time: 47, Output2: 1 At time: 48, Output1: 0

Below is the screenshot of the gtkwave plot of the generated VCD file.