|

- A Logic Circuit Simulation Library in C++ |

|

- A Logic Circuit Simulation Library in C++ |

#include <not.h>

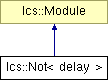

Inheritance diagram for lcs::Not< delay >:

delay indicates the propogation delay from the input to the output of the NOT gate.

Public Member Functions | |

| Not (const Bus< 1 > &output, const InputBus< 1 > &input) | |

| virtual | ~Not () |

| virtual void | onStateChange (int portId) |

Static Public Attributes | |

| static const int | INPUT = 0 |

| static const int | OUTPUT = 1 |

| lcs::Not< delay >::Not | ( | const Bus< 1 > & | output, | |

| const InputBus< 1 > & | input | |||

| ) |

The only meaningfull constructor for the class. A default constructor is not explicitly provided. Moreover, the one synthesized by the compiler is practically useless.

| output | The single line output bus of the gate. | |

| input | The multiline input bus to the gate. | |

| width | The number of lines in the input bus. |

| void lcs::Not< delay >::onStateChange | ( | int | portId | ) | [virtual] |

Propogates the input data line states to the output. This function is called by the input bus line to notify the gate of a lcs::LINE_STATE_CHANGE event. When notified, a NOT operation is performed on the line state of the data line of the input bus and the result is propogated to the single line output bus.

Reimplemented from lcs::Module.

A constant integer which denotes the port id for the input port/bus.

A constant integer which denotes the port id for the output bus/port.