|

- A Logic Circuit Simulation Library in C++ |

|

- A Logic Circuit Simulation Library in C++ |

#include <freqdiv.h>

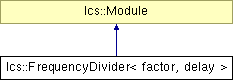

Inheritance diagram for lcs::FrequencyDivider< factor, delay >:

Public Member Functions | |

| FrequencyDivider (const Bus< 1 > &output, const InputBus< 1 > &input) | |

| virtual | ~FrequencyDivider () |

| virtual void | onPosEdge (int portId) |

| virtual void | onNegEdge (int portId) |

| lcs::FrequencyDivider< factor, delay >::FrequencyDivider | ( | const Bus< 1 > & | output, | |

| const InputBus< 1 > & | input | |||

| ) |

The only usefull constructor for the class. The default constructor, if synthesised by the compiler, is practically useless.

| output | The bus of the module. | |

| input | The input bus of the module. |

| virtual lcs::FrequencyDivider< factor, delay >::~FrequencyDivider | ( | ) | [inline, virtual] |

Destructor.

| void lcs::FrequencyDivider< factor, delay >::onNegEdge | ( | int | portId | ) | [virtual] |

A subclass of the class Module should override this function so that it can be notified of a negetive edge on its input busses. If a lcs::LINE_NEG_EDGE event occurs on an input bus, the bus will call this function on the corresponding module object as a notification of the occurance of the event.

Reimplemented from lcs::Module.

| void lcs::FrequencyDivider< factor, delay >::onPosEdge | ( | int | portId | ) | [virtual] |

Function which toggles the output line state at the suitable positive edge. A user of libLCS will never need to use this function directly/explicitly.

Reimplemented from lcs::Module.