|

- A Logic Circuit Simulation Library in C++ |

|

- A Logic Circuit Simulation Library in C++ |

#include <module.h>

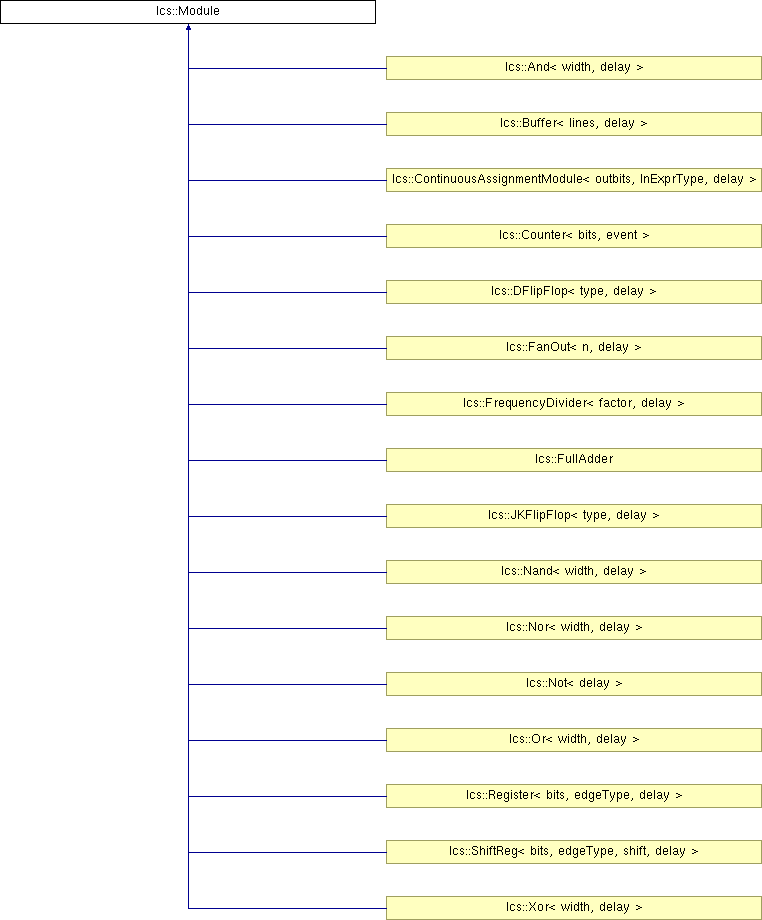

Inheritance diagram for lcs::Module:

Public Member Functions | |

| Module (void) | |

| virtual | ~Module () |

| virtual void | onStateChange (int portId) |

| virtual void | onPosEdge (int portId) |

| virtual void | onNegEdge (int portId) |

| lcs::Module::Module | ( | void | ) | [inline] |

Default constructor.

| virtual lcs::Module::~Module | ( | ) | [inline, virtual] |

Destructor.

| virtual void lcs::Module::onNegEdge | ( | int | portId | ) | [inline, virtual] |

A subclass of the class Module should override this function so that it can be notified of a negetive edge on its input busses. If a lcs::LINE_NEG_EDGE event occurs on an input bus, the bus will call this function on the corresponding module object as a notification of the occurance of the event.

Reimplemented in lcs::Counter< bits, event >, lcs::DFlipFlop< type, delay >, lcs::FrequencyDivider< factor, delay >, lcs::JKFlipFlop< type, delay >, lcs::Register< bits, edgeType, delay >, and lcs::ShiftReg< bits, edgeType, shift, delay >.

| virtual void lcs::Module::onPosEdge | ( | int | portId | ) | [inline, virtual] |

A subclass of the class Module should override this function so that it can be notified of a positive edge on its input busses. If a lcs::LINE_POS_EDGE event occurs on an input bus, the bus will call this function on the corresponding module object as a notification of the occurance of the event.

Reimplemented in lcs::Counter< bits, event >, lcs::DFlipFlop< type, delay >, lcs::FrequencyDivider< factor, delay >, lcs::JKFlipFlop< type, delay >, lcs::Register< bits, edgeType, delay >, and lcs::ShiftReg< bits, edgeType, shift, delay >.

| virtual void lcs::Module::onStateChange | ( | int | portId | ) | [inline, virtual] |

A subclass of the class Module should override this function so that it can be notified of a state change on its input busses. If a lcs::LINE_STATE_CHANGE event occurs on an input bus, the bus will call this function on the corresponding module object as a notification of the occurance of the event.

Reimplemented in lcs::And< width, delay >, lcs::Buffer< lines, delay >, lcs::ContinuousAssignmentModule< outbits, InExprType, delay >, lcs::Counter< bits, event >, lcs::DFlipFlop< type, delay >, lcs::FullAdder, lcs::FanOut< n, delay >, lcs::JKFlipFlop< type, delay >, lcs::Nand< width, delay >, lcs::Nor< width, delay >, lcs::Not< delay >, lcs::Or< width, delay >, and lcs::Xor< width, delay >.