|

- A Logic Circuit Simulation Library in C++ |

|

- A Logic Circuit Simulation Library in C++ |

#include <shiftreg.h>

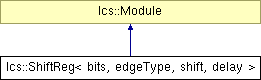

Inheritance diagram for lcs::ShiftReg< bits, edgeType, shift, delay >:

| bits | The number of bits in the register. | |

| edgeType | The edge type at which triggers a shift. | |

| shift | This template argument denotes whether a left shift, or a right shift has to be performed. | |

| delay | The delay with which the shift should be performed after the triggering edge occurs at the clock input. This can considered as a propogation delay. |

Public Member Functions | |

| ShiftReg (const Bus< bits > &out, const InputBus< 1 > &in, const InputBus< 1 > &clk) | |

| virtual | ~ShiftReg () |

| virtual void | onPosEdge (int portId) |

| virtual void | onNegEdge (int portId) |

| const LineState | operator[] (const int &i) |

| lcs::ShiftReg< bits, edgeType, shift, delay >::ShiftReg | ( | const Bus< bits > & | out, | |

| const InputBus< 1 > & | in, | |||

| const InputBus< 1 > & | clk | |||

| ) |

Constructor. The only usefull constructor.

| out | The output bus, or the read bus, of the register. | |

| in | The input stream to the shift register. |

| lcs::ShiftReg< bits, edgeType, shift, delay >::~ShiftReg | ( | ) | [virtual] |

Destructor.

| virtual void lcs::ShiftReg< bits, edgeType, shift, delay >::onNegEdge | ( | int | portId | ) | [inline, virtual] |

Internal function which will never be used by a user of libLCS.

Reimplemented from lcs::Module.

| virtual void lcs::ShiftReg< bits, edgeType, shift, delay >::onPosEdge | ( | int | portId | ) | [inline, virtual] |

Internal function which will never be used by a user of libLCS.

Reimplemented from lcs::Module.

| const LineState lcs::ShiftReg< bits, edgeType, shift, delay >::operator[] | ( | const int & | i | ) | [inline] |

An overloaded read only operator[] which can be used to read the line state of the i-th bit of the register.